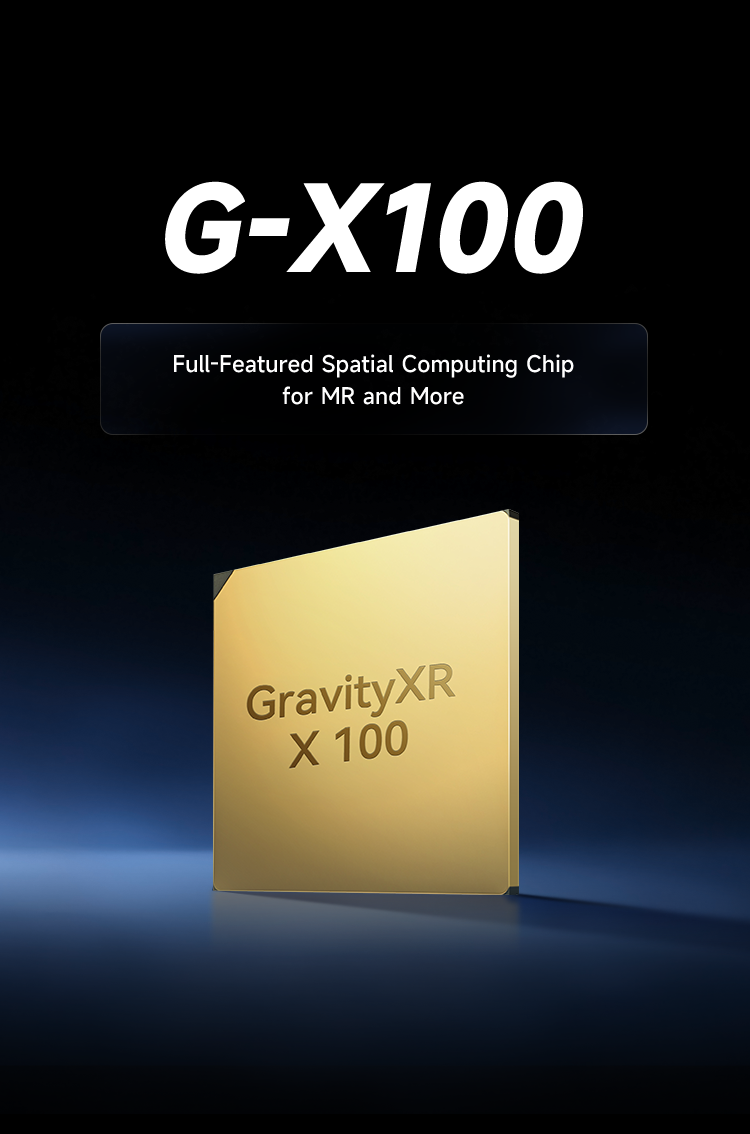

First full-featured spatial

computing chip

-

First spatially computing chip with

heterogeneous packaging based on

Chiplet architecture -

World Record: The chip achieves

video see through latency of 9ms -

Equivalent spatial

computing performance

of 200 TOPS and storage

bandwidth of 70 GB/s -

Enabling miniaturized full-featured

spatial computing devices with power consumption as low as 3W -

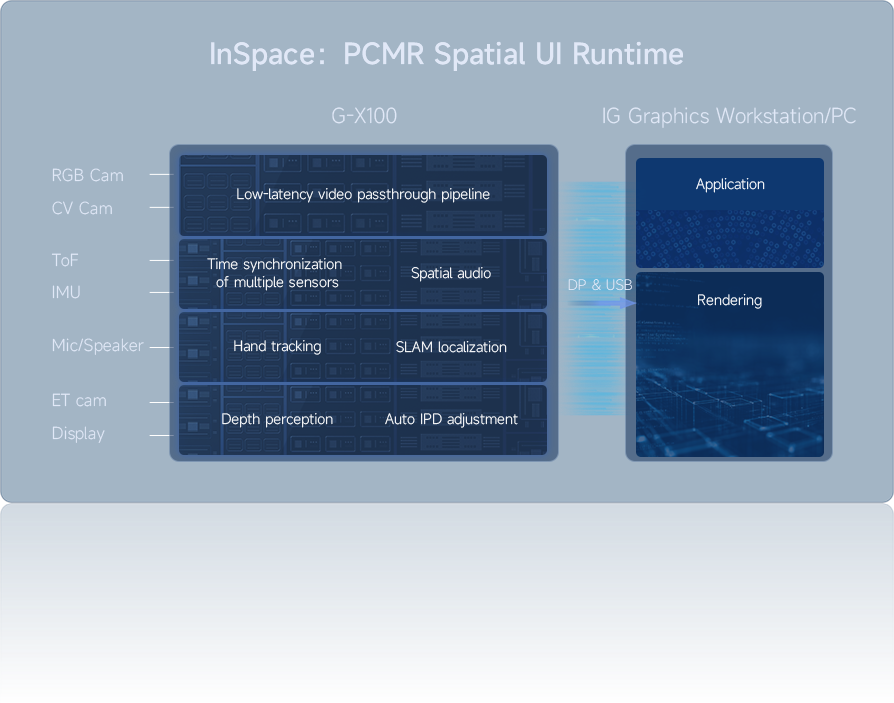

First to support optimal split computing,

compatible with cross-chip platforms and

cross-OS software ecosystems

-

Full-Link FoveatedRendering technology for MR

Full-Link FoveatedRendering technology for MR -

Universal Spatial

Universal Spatial

Computing EcosystemSupports multiple spatial computing terminals and AP architecturesFlexible computing power deployment solutionsComplete development, production, and debugging toolchain -

Advanced ProcessLow-power Chiplet architecture

Advanced ProcessLow-power Chiplet architecture -

40 TOPS NPU

40 TOPS NPU

(AI-Enabled)Supported functions:- Eye tracking

- Hand tracking

- Display

- ISP

-

Micro-OLED

Micro-OLED

Image Optimization

Algorithm -

Reverse Perspective

Reverse Perspective

& Digital HumanMulti-view parallel rendering and

multi-layer hybrid display -

Natural Eye-Hand

Natural Eye-Hand

InteractionSupports multiple interaction methods:

Eye tracking, Hand tracking, etc. -

Dual 16MPRGB camera input and image processing

Dual 16MPRGB camera input and image processing -

8K/120HzUltra-high-definition mixed reality display output

8K/120HzUltra-high-definition mixed reality display output -

13 Channels of

13 Channels of

Multi-Type Sensor

Fusion -

6DoFSupports multiple spatial positioning

6DoFSupports multiple spatial positioning

algorithms -

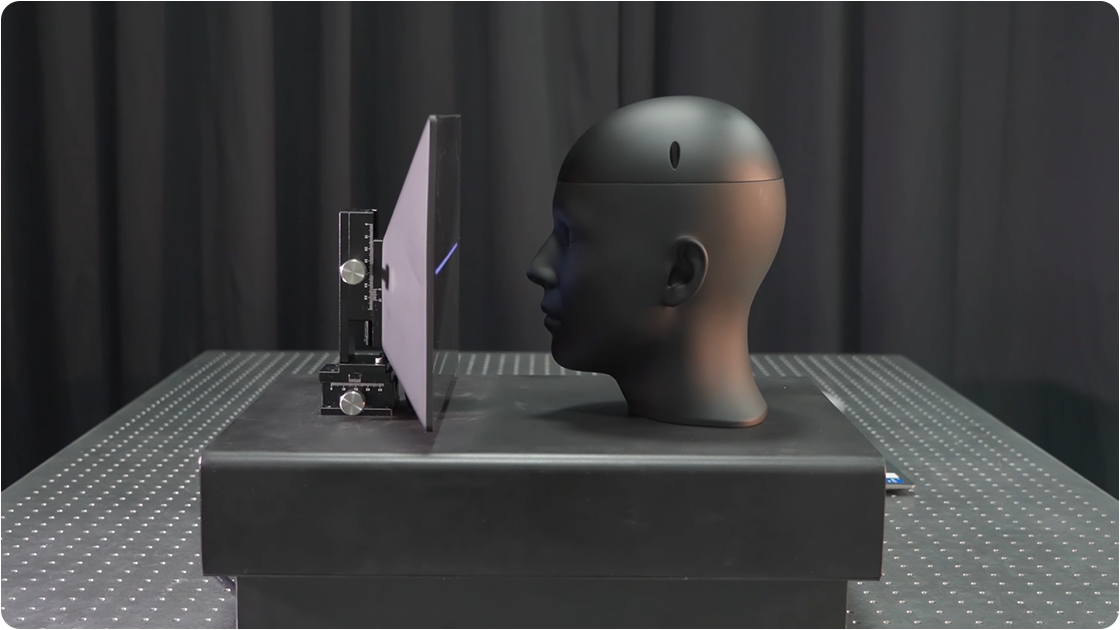

9msLowest VST Latency

9msLowest VST Latency -

10-Core DSP

10-Core DSP -

Real-Time Depth

Real-Time Depth

& 3D Reconstruction

Instant Video See-through

9ms VST Latency,No Motion Sickness

-

Stunning Visual Fidelity

Display & Fusion System8K 120Hz display output

Professional Micro-OLED display pipeline

High-definition HDR pipeline

Physical fusion engine

Seamless Immersion Adjustment -

Omniscient Perception

Perception SubsystemDual 16MP RGB cameras

13-channel sensors

10-core DSP

40 TOPS NPU

Spatial positioning & 3D perception

Spatial hand-eye interaction

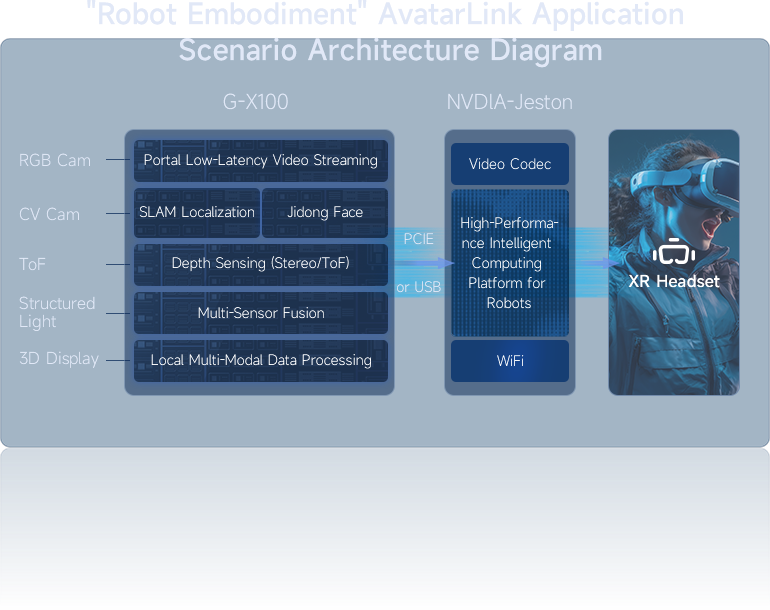

Robotics Remote Vision & Operation

Windows MR